# 1/4-Inch 2Mp System-On-A-Chip (SOC) CMOS Digital Image Sensor

# MT9D112

For the latest data sheet, refer to Aptina's Web site: www.aptina.com

### **Features**

- DigitalClarity<sup>®</sup> CMOS imaging technology

- Superior low-light performance

- Ultra-low-power, low-cost

- Internal master clock generated by on-chip phaselocked loop (PLL) oscillator

- Electronic rolling shutter (ERS), progressive scan

- Integrated image flow processor (IFP) for single-die camera module

- Automatic image correction and enhancement, including 4-channel lens shading correction with independent corner correction

- · Arbitrary image scaling with anti-aliasing

- Integrated microcontroller for flexibility

- Two-wire serial interface providing access to registers and microcontroller memory

- Selectable output data format: YCbCr, 565RGB, 555RGB, 444RGB, processed Bayer, RAW8, and RAW10 bit

- · Output FIFO for data rate equalization

- Programmable I/O slew rate

- Parallel and serial MIPI data output

- Xenon and LED flash support with fast exposure adaptation

- Flexible support for external auto focus, optical zoom, and mechanical shutter

- Independently configurable gamma correction

# **Applications**

- Cellular phones

- PC cameras

- PDAs

Table 1: Key Performance Parameters

| Parameter             |         | Value                                 |  |

|-----------------------|---------|---------------------------------------|--|

| Optical format        |         | 1/4-inch (4:3)                        |  |

| Full resolution       |         | 1600 x 1200 pixels (UXGA)             |  |

| Pixel size            |         | 2.2 x 2.2μm                           |  |

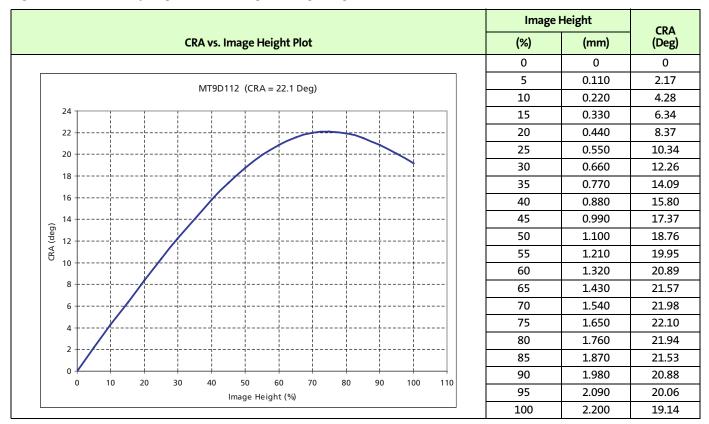

| Chief ray angle       |         | 22.1 deg maximum at 75% image         |  |

|                       |         | height                                |  |

|                       |         | 27.0 deg maximum at 80% image         |  |

|                       |         | height                                |  |

| Color filter array    |         | RGB Bayer pattern                     |  |

| Active pixel arra     | ay area | 3.56mm x 2.68mm                       |  |

| Shutter type          |         | Electronic rolling shutter (ERS) with |  |

|                       |         | global reset                          |  |

| Input clock freq      | -       | 6–54 MHz                              |  |

| Maximum fram          | e rate  | 15 fps at full resolution,            |  |

|                       |         | 24 fps in preview mode,               |  |

|                       |         | 30 fps in video mode                  |  |

| Maximum data          | rate/   | 80 Mb/s                               |  |

| master clock          |         | 6 MHz to 80 MHz                       |  |

|                       | Analog  | 2.5-3.1V                              |  |

|                       | Digital | 1.7–1.95V                             |  |

| Supply voltage        | 1/0     | 1.7–1.95V or 2.5–3.1V                 |  |

|                       | PLL     | 2.5-3.1V                              |  |

|                       | AF      | 1.7–3.1V                              |  |

| ADC resolution        |         | 10-bit, on-die                        |  |

| Responsivity          |         | 0.53 V/lux-sec (preliminary)          |  |

| Dynamic range         |         | 59.5dB (preliminary)                  |  |

| SNRMAX                |         | 37.7dB (preliminary)                  |  |

|                       |         | 245mW at 15 fps, full resolution      |  |

| Power                 |         | 230mW at 30 fps, video mode           |  |

| consumption           |         | 168mW at 24 fps, preview mode         |  |

|                       |         | 10μW, standby/shutdown                |  |

| Operating temperature |         | –30°C to +70°C (at junction)          |  |

| Packaging             |         | Bare die                              |  |

# **Ordering Information**

Table 2: Available Part Numbers

| Part Number          | Description             |

|----------------------|-------------------------|

| MT9D112D00STCK15AC1  | Bare die (22.1 deg CRA) |

| MT9D112D00STCZK15AC1 | Bare die (27.0 deg CRA) |

# **Table of Contents**

| Features                                        |     |

|-------------------------------------------------|-----|

| Applications                                    |     |

| Ordering Information                            |     |

| General Description                             |     |

| MT9D112 Overview                                |     |

| Signal Description                              | 9   |

| Typical Connections                             |     |

| Architecture Overview                           |     |

| Sensor Core Description                         | .11 |

| Pixel Array                                     | .12 |

| Pixel Array Structure                           | .12 |

| Default Readout Order                           | .13 |

| Analog Processing                               | .14 |

| Analog Readout Channel                          | .14 |

| Timing and Control                              | .14 |

| Gain Options                                    |     |

| Integration Time                                |     |

| PLL                                             |     |

| PLL-Generated Master Clock                      |     |

| PLL Setup                                       |     |

| Readout Options                                 |     |

| Window Size                                     |     |

| Readout Modes                                   |     |

| Horizontal Mirror                               |     |

| Vertical Flip                                   |     |

| Column and Row Skip                             |     |

| Programming Restrictions when Skipping          |     |

| Binning                                         |     |

| Binning Limitations                             |     |

| Raw Data Format                                 |     |

| Raw Data Timing                                 |     |

| SOC Description                                 |     |

| Image Flow Processor                            |     |

| Test Patterns                                   |     |

| First Black Level Subtraction and Digital Gain  |     |

| Lens Shading Correction                         |     |

| Lens Correction Zones                           |     |

| Defect Correction and Noise Reduction.          | .20 |

| Color Interpolation and Edge Detection          |     |

| Second Black Level Correction                   |     |

| Color Correction and Aperture Correction        |     |

| •                                               |     |

| Image Cropping    Contrast and Gamma Correction |     |

|                                                 |     |

| S-Curve                                         |     |

| RGB to YUV Conversion                           |     |

| Color Kill                                      |     |

| YUV Color Filter                                |     |

| Image Scaling                                   |     |

| YUV-to-RGB/YUV Conversion and Output Formatting |     |

| Color Conversion Formulas                       |     |

| Y'U'V'                                          | .31 |

| WILLWILL . DODE 1                                | 00 |

|--------------------------------------------------|----|

| Y'U'V' Using sRGB Formulas                       |    |

| Output Interface                                 |    |

| Parallel and MIPI Output                         |    |

| Output Format and Timing                         |    |

| YUV/RGB Uncompressed Output                      |    |

| Uncompressed YUV/RGB Data Ordering               |    |

| FIFO                                             |    |

| Watermark                                        |    |

| Camera Control                                   |    |

| General Purpose I/Os                             |    |

| Output Enable Control                            |    |

| Trigger ControlStreaming/Standby Control         | 30 |

|                                                  |    |

| Firmware Architecture                            |    |

| Sequencer                                        |    |

| Context and Operational Modes                    |    |

| Preview Mode                                     |    |

| Still Capture and Video Modes                    |    |

| Snapshot and Flash                               |    |

| Video                                            |    |

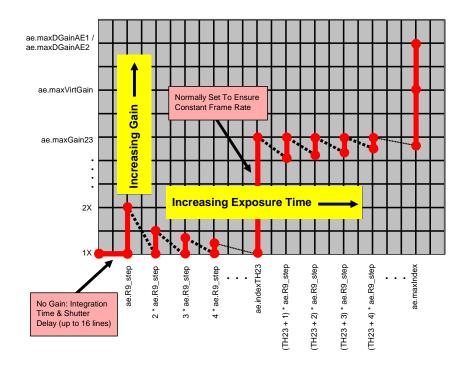

| Auto Exposure                                    |    |

| Preview Mode                                     |    |

| Evaluative Algorithm (MDR)                       |    |

| Accelerated Settling During Overexposure         | 40 |

| Exposure Control.                                |    |

| AE MDR Mode.                                     |    |

| Auto White Balance                               |    |

| Flicker Detection                                |    |

| Auto Focus                                       |    |

| Algorithm                                        |    |

| Modes                                            |    |

| Lens Actuator Interface                          |    |

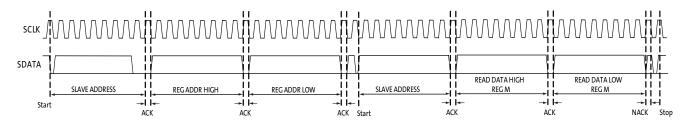

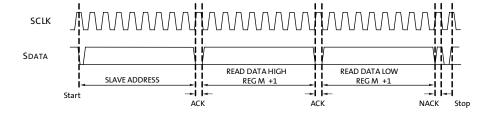

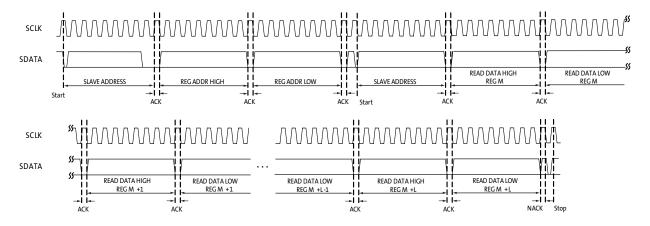

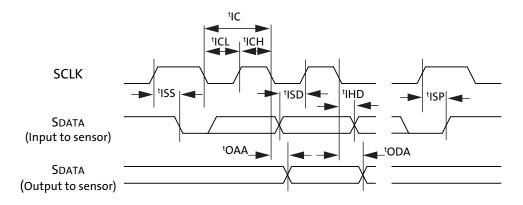

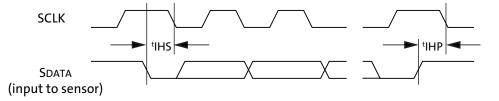

| Two-Wire Serial Interface                        |    |

| Protocol                                         |    |

| Start Condition                                  |    |

| Stop Condition                                   |    |

| Data Transfer                                    |    |

| Slave Address/Data Direction Byte                |    |

| Message Byte                                     |    |

| Acknowledge Bit                                  |    |

| No-Acknowledge Bit                               |    |

| Typical Serial Transfer                          |    |

| Single Read from Random Location.                |    |

| Single Read from Current Location                |    |

| Sequential Read, Start from Random Location      |    |

| Sequential Read, Start from Current Location     |    |

| Single Write to Random Location                  |    |

| Sequential Write, Start at Random Location       |    |

| Registers and Variables                          |    |

| How to Access Registers and Variables            |    |

| Registers                                        |    |

| VariablesSpecial Function Registers and MCU SRAM | 51 |

| Special Function Registers and MCU SRAM          | 3/ |

| Core Registers                                           | 53 |

|----------------------------------------------------------|----|

| Double-buffered Registers                                |    |

| Bad Frames                                               |    |

| Changes to Integration Time                              | 53 |

| Changes to Gain Settings                                 |    |

| Timing Specifications                                    |    |

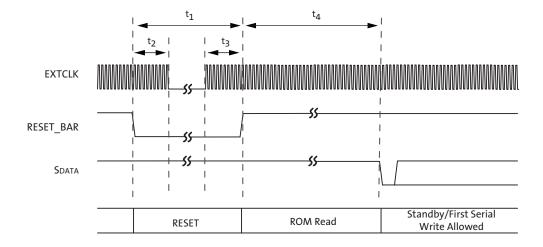

| Power-up Sequence                                        |    |

| Hard Reset                                               |    |

| Soft Reset                                               | 56 |

| Standby Sequences                                        | 57 |

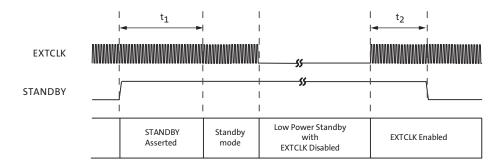

| Hard Standby                                             |    |

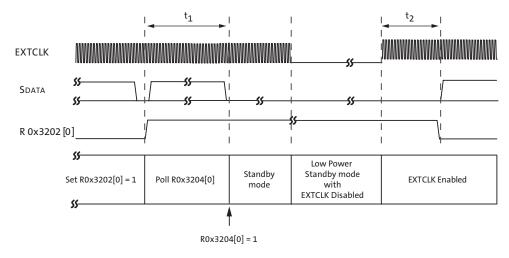

| Soft Standby (Two-wire Serial Interface)                 | 58 |

| How to Inhibit Standby Entry                             | 59 |

| How to Synchronize Standby with End of Frame             |    |

| How to Reproduce the Sequence of Soft Standby in DevWare |    |

| Pin States                                               |    |

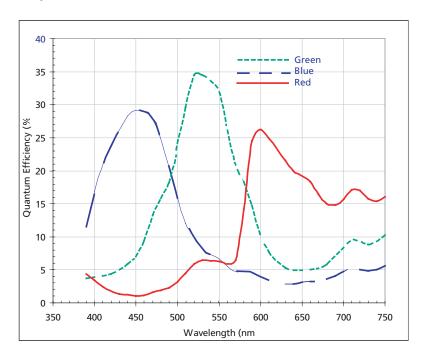

| Spectral Characteristics                                 | 63 |

| Electrical Specifications                                |    |

| Revision History                                         | 70 |

# **List of Figures**

| Figure 1:  | Typical Configuration (connections)                                                   | .10 |

|------------|---------------------------------------------------------------------------------------|-----|

| Figure 2:  | SOC Block Diagram                                                                     | .11 |

| Figure 3:  | Sensor Core Block Diagram                                                             |     |

| Figure 4:  | Pixel Array                                                                           |     |

| Figure 5:  | Pixel Color Pattern Detail (Top Right Corner)                                         | .13 |

| Figure 6:  | Imaging a Scene                                                                       | .13 |

| Figure 7:  | 6 Pixels in Normal and Column Mirror Readout Modes                                    |     |

| Figure 8:  | 6 Rows in Normal and Row Mirror Readout Modes                                         |     |

| Figure 9:  | 8 Pixels in Normal and Column Skip 2X Readout Modes                                   | .18 |

| Figure 10: | Pixel Readout (no skipping)                                                           | .18 |

| Figure 11: | Pixel Readout (x_odd_inc=3, y_odd_inc=1)                                              | .18 |

| Figure 12: | Pixel Readout (x_odd_inc=1, y_odd_inc=3)                                              | .19 |

| Figure 13: | Pixel Readout (x_odd_inc=3, y_odd_inc=3)                                              | .19 |

| Figure 14: | Pixel Readout (x_odd_inc=3, y_odd_inc=1, x_bin=1)                                     | .20 |

| Figure 15: | Pixel Readout (x_odd_inc=3, y_odd_inc=3, x_ybin=1)                                    | .21 |

| Figure 16: | Pixel Data Timing Example                                                             | .22 |

| Figure 17: | Pixel Data Timing Example                                                             | .22 |

| Figure 18: | Row Timing and FRAME_VALID/LINE_VALID Signals                                         | .23 |

| Figure 19: | Color Pipeline                                                                        | .24 |

| Figure 20: | Test Patterns                                                                         |     |

| Figure 21: | Lens Correction Zones                                                                 |     |

| Figure 22: | Gamma Correction Curve                                                                | .29 |

| Figure 23: | Contrast "S" Curve                                                                    |     |

| Figure 24: | Timing of Uncompressed Full Frame Output or Decimated Output Passing Through the FIFO | .33 |

| Figure 25: | Example of Timing for Non-Decimated Uncompressed Output Bypassing Output FIFO         | .34 |

| Figure 26: | Software Architecture                                                                 |     |

| Figure 27: | Gain vs. Exposure                                                                     |     |

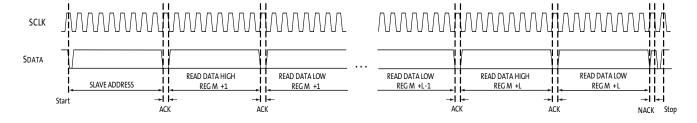

| Figure 28: | Single Read from Random Location                                                      |     |

| Figure 29: | Single Read from Current Location                                                     |     |

| Figure 30: | Sequential Read, Start from Random Location                                           |     |

| Figure 31: | Sequential Read, Start from Current Location                                          | .49 |

| Figure 32: | Single Write to Random Location                                                       | .50 |

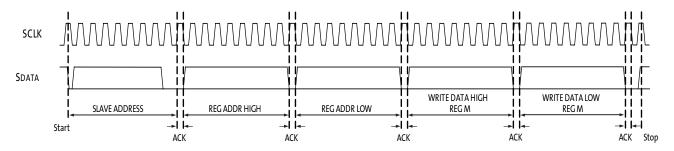

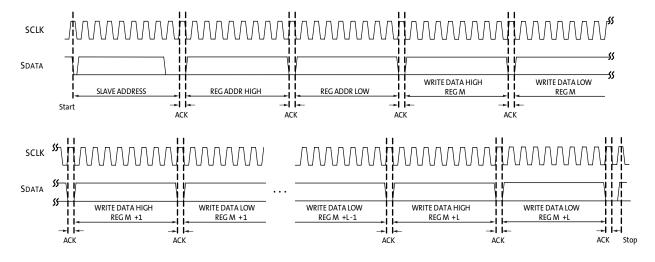

| Figure 33: | Sequential Write, Start at Random Location                                            | .50 |

| Figure 34: | Internal Power-On Reset                                                               |     |

| Figure 35: | Hard Reset                                                                            |     |

| Figure 36: | Hard Standby                                                                          |     |

| Figure 37: | Soft Standby                                                                          |     |

| Figure 38: | Chief Ray Angle (CRA 22.1 Deg) vs. Image Height                                       | .63 |

| Figure 39: | Chief Ray Angle (27.0 Deg CRA) vs. Image Height                                       |     |

| Figure 40: | Quantum Efficiency                                                                    | .64 |

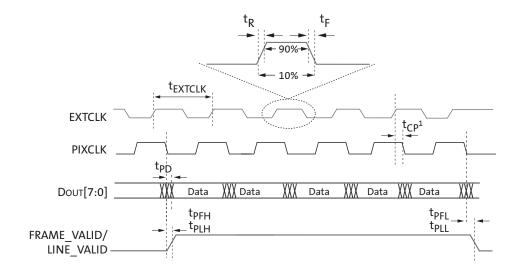

| Figure 41: | I/O Timing Diagram                                                                    |     |

| Figure 42: | Two-Wire Serial Interface Timing                                                      |     |

| Figure 43: | Two-Wire Serial Interface Start and Stop Timing                                       | ß۵  |

# **List of Tables**

| Table 1:  | Key Performance Parameters                      |    |

|-----------|-------------------------------------------------|----|

| Table 2:  | Available Part Numbers                          |    |

| Table 3:  | Signal Description                              |    |

| Table 4:  | Frequency Parameters                            | 16 |

| Table 5:  | Row Address Sequencing                          |    |

| Table 6:  | Row Timing Parameters                           |    |

| Table 7:  | Gamma Settings                                  |    |

| Table 8:  | Contrast Values                                 |    |

| Table 9:  | YCrCb Output Data Ordering                      |    |

| Table 10: | RGB Ordering in Default Mode                    |    |

| Table 11: | 2-Byte RGB Format                               |    |

| Table 12: | Output Enable Control                           |    |

| Table 13: | Trigger Control                                 |    |

| Table 14: | Streaming/STANDBY                               |    |

| Table 15: | POR Parameters                                  |    |

| Table 16: | Hard Reset                                      |    |

| Table 17: | Hard Standby                                    |    |

| Table 18: | Soft Standby                                    |    |

| Table 19: | Summary of Standby States                       |    |

| Table 20: | Pin States During Conditions                    |    |

| Table 21: | AC Electrical Characteristics                   |    |

| Table 22: | I/O Parameters                                  | 67 |

| Table 23: | DC Electrical Definitions and Characteristics   |    |

| Table 24: | Absolute Maximum Ratings                        |    |

| Table 25: | Two-Wire Serial Interface Timing Specifications |    |

# **General Description**

The Aptina  $^{\circledR}$  MT9D112 is a 1/4-inch 2Mp CMOS image sensor with an integrated advanced camera system. This camera system features a microcontroller (MCU), a sophisticated image flow processor (IFP), and both parallel and serial mobile industry processor interface (MIPI) interfaces. It also includes a programmable general purpose I/O module (GPIO), which can be used to control external auto focus (AF), optical zoom, or mechanical shutter. The microcontroller manages all components of the camera system and sets key operation parameters for the sensor core to optimize the quality of raw image data entering the IFP. The sensor core consists of an active pixel array of 1616 x 1216 pixels, programmable timing and control circuitry including a PLL and external flash support, analog signal chain with automatic offset correction and programmable gain, and two 10-bit analog-to-digital converters (ADC). The entire system-on-a-chip (SOC) has ultra-low power requirements and superior low light performance that is particularly suitable for mobile applications. The MT9D112 is based on DigitalClarity<sup>®</sup> Technology—Aptina's breakthrough low-noise CMOS imaging technology that achieves near-CCD image quality (based on signal-to-noise ratio and lowlight sensitivity) while maintaining the inherent size, cost, power consumption, and integration advantages of CMOS.

### MT9D112 Overview

The MT9D112 has a color image sensor with a Bayer color filter arrangement and a 2Mp active-pixel array with electronic rolling shutter and global reset. The sensor core readout is 10-bit and supports skipping, binning and can be flipped and/or mirrored. The sensor core also supports separate analog and digital gain for all four color channels (R, Gr, Gb, B).

The MT9D112 also has an embedded phase-locked loop oscillator (PLL) that can generate the internal sensor clock from the common wireless system clock. When in use, the PLL adjusts the incoming clock frequency up, allowing the MT9D112 to run at almost any desired resolution and frame rate within the sensor's capabilities. The PLL can be bypassed and powered down to reduce power consumption.

Low power consumption is a very important requirement for all components of wireless devices. The MT9D112 has numerous power-conserving features, including soft and hard standby modes, as well as an external SHUTDOWN pin that allows the internal power bus to be disabled.

Another important consideration for wireless devices is their electromagnetic interface (EMI). The MT9D112 can be used with either a serial MIPI interface or the parallel data output interface which has a programmable I/O slew rate to minimize EMI and an output FIFO to eliminate output data bursts.

The advanced image flow processor and flexible programmability of the MT9D112 provide a variety of ways to enhance and optimize the image sensor performance. Built-in optimization algorithms enable the MT9D112 to operate at factory settings as a fully automatic, highly adaptable camera; however, most of its settings are user-programmable.

These algorithms include black level conditioning, lens shading correction, defect correction, noise reduction, color interpolation, edge detection, color correction, aperture correction, and image formatting such as cropping and scaling.

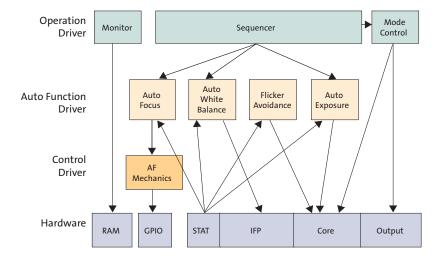

The MT9D112 also includes a sequencer that coordinates all events triggered by the user. The sequencer manages auto focus, auto white balance, flicker detection, and auto exposure for the different operating modes which include preview, still capture, video, and snapshot with flash.

A two-wire serial register interface bus enables read/write access to control registers, variables, and special function registers within the MT9D112. The hardware registers are grouped internally by pages and include sensor core controls, color pipeline controls, and output controls. Variables are located in the microcontroller's RAM memory and are used for drivers such as the auto exposure (AE), auto white balance (AWB), and auto focus (AF). Special function registers are registers connected to the local bus of the microcontroller and include GPIO and the waveform generator.

The general purpose I/O can be configured to allow the user to output a flash or shutter pulse or to achieve 10-bit parallel output, or they can be configured as inputs to enable the user to use features such as an external trigger.

# **Signal Description**

Table 3 provides the signal descriptions for the MT9D112.

# Table 3: Signal Description

| Name         | Туре   | Description                                                                                                              |  |

|--------------|--------|--------------------------------------------------------------------------------------------------------------------------|--|

| SHUTDOWN     | Input  | Power down VDD, active HIGH.                                                                                             |  |

| TEST_EN      | Input  | Reserved for factory test. Tie to digital ground during normal operation (can leave floating if not used).               |  |

| STANDBY      | Input  | Controls sensor standby mode, active HIGH.                                                                               |  |

| SCLK         | Input  | Two-wire serial interface clock.                                                                                         |  |

| SADDR        | Input  | Selects device address for the two-wire serial interface. The address is 0x78 when SADDR is tied LOW, 0x7A if tied HIGH. |  |

| RESET_BAR    | Input  | Master reset signal, active LOW.                                                                                         |  |

| EXTCLK       | Input  | Input clock signal 6–54 MHz.                                                                                             |  |

| GPIO[3:0]    | I/O    | General purpose digital I/O, could be configured for FLASH/SHUTTER/DOUT_LSB0/DOUT_LSB1/MODULE_ID/OE_BAR/TRIGGER.         |  |

| Sdata        | I/O    | Two-wire serial interface data.                                                                                          |  |

| GPIO_AF[7:0] | I/O    | General purpose digital I/O. Used for auto focus function (can leave floating if not used).                              |  |

| Dоuт[7:0]    | Output | Eight-bit image data output or most significant bits (MSB) of 10-bit sensor bypass mode.                                 |  |

| DATA_OUT_N   | Output | Differential MIPI data (sub-LVDS, negative) (must leave floating if not used).                                           |  |

| DATA_OUT_P   | Output | Differential MIPI data (sub-LVDS, positive) (must leave floating if not used).                                           |  |

| CLK_OUT_N    | Output | Differential MIPI clock (sub-LVDS, negative) (must leave floating if not used).                                          |  |

| CLK_OUT_P    | Output | Differential MIPI clock (sub-LVDS, positive) (must leave floating if not used).                                          |  |

| PIXCLK       | Output | Pixel clock. Used for sampling Dout, FRAME_VALID, and LINE_VALID.                                                        |  |

| LINE_VALID   | Output | Identifies lines in the active image.                                                                                    |  |

| FRAME_VALID  | Output | Identifies rows in the active image.                                                                                     |  |

| VDD          | Supply | Digital power (1.8V).                                                                                                    |  |

| VAA_PIX      | Supply | Pixel array power (2.8V).                                                                                                |  |

| VAA          | Supply | Analog power (2.8V).                                                                                                     |  |

| VDD_PLL      | Supply | PLL power (2.8V).                                                                                                        |  |

| VDD_IO       | Supply | I/O power supply (1.7–1.95V or 2.5–3.1V).                                                                                |  |

| GND_IO       | Supply | I/O ground.                                                                                                              |  |

| DGND         | Supply | Digital, I/O, and PLL ground.                                                                                            |  |

| AGND         | Supply | Analog ground.                                                                                                           |  |

| VDD_AF       | Supply | I/O power supply for GPIO_AF[7:0] pads (can leave floating if not used).                                                 |  |

| GND_AF       | Supply | IO ground for GPIO_AF[7:0].                                                                                              |  |

# **Typical Connections**

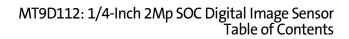

Figure 1 shows typical MT9D112 device connections. For low-noise operation, the MT9D112 requires separate power supplies for analog and digital. Incoming digital and analog ground conductors can be tied together next to the die. Both power supply rails should be decoupled to ground using capacitors as close as possible to the die. The use of inductance filters is not recommended on the power supplies or output signals.

The MT9D112 also supports different digital core (VDD/DGND) and I/O power (VDD\_IO/DGND) power domains that can be at different voltages. The PLL requires a clean power source (VDDPLL).

Figure 1: Typical Configuration (connections)

It is recommended that  $0.1\mu F$  and  $1\mu F$  decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design capacides the pad.

Notes:

- 1. This typical configuration shows only one scenario out of multiple possible variations for this sensor.

- 2. If auto focus is not required, the following pads can be left floating: VDD\_AF, GND\_AF, and GPIO\_AF.

- 3. The GPIO pads can serve multiple functions and can be reconfigured. The function and direction will vary by application.

- 4. Only one of the output modes (serial or parallel) can be used at any time.

- 5. A resister value of 1.5K $\Omega$  is recommended for the two-wire serial interface RPULL-UP, however, a greater value may be used for slower transmission speed.

- 6. All inputs must be configured with VDD IO.

- 7. VAA and VAA\_PIX must be tied together.

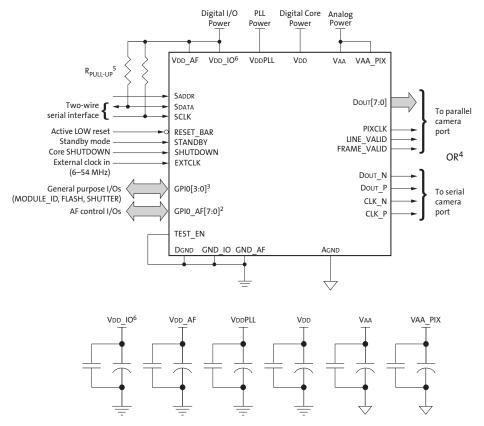

### Architecture Overview

The MT9D112 combines a 2Mp sensor core together with an image flow processor (IFP) to form a stand-alone solution that includes both image acquisition and processing. The processed image data is transmitted to the host-system either via a parallel bus or a serial data interface through the output interface. In normal operation, an integrated microcontroller (MCU) controls most aspects of operation autonomously. This includes the control over key internal registers for both sensor core and the IFP settings. However, registers can be controlled by the user as well. This can be achieved by either controlling registers through the MCU, or by disabling the MCU for direct control.

Figure 2: SOC Block Diagram

# **Sensor Core Description**

The sensor core of the MT9D112 is a progressive-scan sensor that generates a stream of pixel data at a constant frame rate, qualified by LINE\_VALID and FRAME\_VALID. The maximum pixel rate is 40 megapixels/second, corresponding to a pixel clock rate of 80 MHz. Figure 3 on page 12 shows a block diagram of the sensor core. It includes a 2-megapixel active-pixel array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in the row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. Once a row has been read, the data from the columns is sequenced through an analog signal chain (providing offset correction and gain), and then through an ADC. The output from the ADC is a 10-bit value for each pixel in the array.

The pixel array contains optically active and light-shielded (dark) pixels. The dark pixels are used to provide data for the offset-correction algorithms (black level control).

The sensor core contains a set of control and status registers that can be used to control many aspects of the sensor behavior including the frame size, exposure, and gain setting. These registers are controlled by the SOC firmware and can be accessed through the two-wire serial interface. Note that register values written to the sensor core may be overwritten by firmware.

The output from the core is a Bayer pattern; alternate rows are a sequence of either green/red pixels or blue/green pixels. The offset and gain stages of the analog signal chain provide per-color control of the pixel data.

A flash strobe output signal is provided to allow an external xenon or LED light source to synchronize with the sensor exposure time. Additional I/O signals support the provision of an external mechanical shutter.

Figure 3: Sensor Core Block Diagram

# **Pixel Array**

### **Pixel Array Structure**

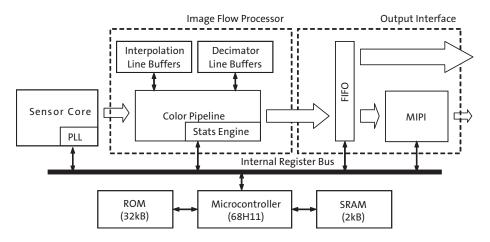

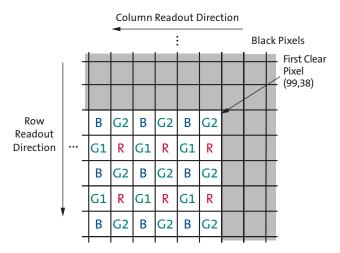

The sensor core pixel array is configured as 1,722 columns by 1,262 rows (shown in Figure 4). The first 100 columns and the first 39 rows of pixels are optically black and are used for the automatic black level adjustment; the last 6 columns are also optically black.

The optically active pixels are used as follows: In default mode a UXGA image (1,616 columns by 1,216 rows) is generated, starting at row 40, column 101. An 8-pixel boundary of active pixels is enabled around the image to avoid boundary effects during color interpolation and correction.

Figure 4: Pixel Array

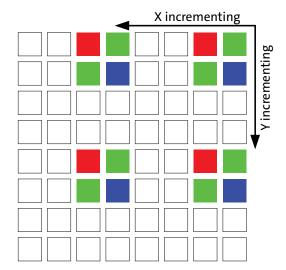

The sensor core uses a Bayer color pattern, as shown in Figure 5. The even-numbered rows contain green and red color pixels; odd-numbered rows contain blue and green color pixels. Even-numbered columns contain green and blue color pixels; odd-numbered columns contain red and green color pixels.

Figure 5: Pixel Color Pattern Detail (Top Right Corner)

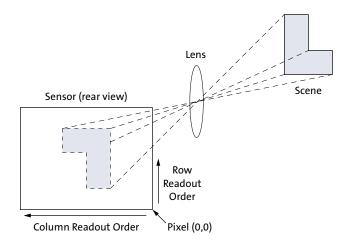

### **Default Readout Order**

By convention, the sensor core pixel array is shown with pixel (0,0) in the top right-hand corner (see Figure 5). This reflects the actual layout of the array on the die. When the sensor is imaging in a system, the active surface of the sensor faces the scene as shown in Figure 6.

When the image is read out of the sensor, it is read one row at a time, with the rows and columns sequenced. By convention, data from the sensor is shown with the first pixel read out—pixel (99,38) in the case of the sensor core—in the top lefthand corner.

Figure 6: Imaging a Scene

# **Analog Processing**

### **Analog Readout Channel**

The sensor core features two identical analog readout channels as shown in Figure 3 on page 12. The readout channel consists of two gain stages, a sample-and-hold stage with black level calibration capability, and a 10-bit ADC.

# **Timing and Control**

### **Gain Options**

The MT9D112 provides per-color gain control as well as the option of global gain control. Per-color and global gain control can be used interchangeably. A write to a global gain register is aliased as a write of the same data to the four associated color-dependent gain registers.

Integer digital gains in the range 0–7 can be programmed. A digital gain of "0" sets all pixel values to 0 (the pixel data will simply represent the value applied by the pedestal block). Gain settings are updated every frame by the MCU auto feature; to make manual adjustments to gain settings, the MCU auto features must be disabled.

### **Integration Time**

The integration (exposure) time of the MT9D112 is controlled by the fine\_integration\_time and coarse\_integration\_time registers. While coarse integration time controls the integration duration steps of lines, the fine time allows for sub-line accuracy. Integration time is updated every frame by the MCU auto feature; to make manual adjustments to integration time, the MCU auto features must be disabled.

The limits for the fine integration time are defined by:

$sensor\_fine\_IT\_min\_A/B \le fine\_integration\_time \le (sensor\_line\_length\_pck\_A/B-sensor\_fine\_IT\_max\_margin\_A/B)$   $Course\ integration\ time\ is < frame\_length\_lines\_margin.$

The actual integration time is given by:

$$integration\_time = \frac{((coarse\_integration\_time \ x \ line\_length\_pck) + fine\_integration\_time)}{vt\_pix\_clk\_freq\_mhz/1x10^6}$$

(EQ 1)

line\_length\_pck is the value of R0x300C

The minimum allowable value for line\_length\_pck is given by the line\_length\_pck> =  $((x_addr_end - x_addr_start + 1)/xskip) + min_line_blanking_pck.$

min\_line\_blanking\_pck is 476 in full resolution mode, 743 in high-power preview mode, and 442 in low-power preview mode.

coarse\_integration\_time is value of R0x3012

fine\_integration\_time is value of R0x3014

x\_addr\_end is a value of R0x3008

x\_addr\_start is a value of R0x3004

xskip is a value of R0x3016[7:5]

### vt\_pix\_clk\_freq\_mhz is MCLK/2

It is fundamental to the operation of an electronic rolling shutter (ERS) that it is not possible to set an integration time that is greater than the frame time. Unlike earlier Aptina Imaging parts, setting an integration time that is greater than the frame time does not affect the frame time; the behavior is undefined. On the MT9D112, it is necessary to reprogram the frame time (frame\_length\_lines) in order to make longer exposure times available. Long integration times increase the likelihood of image degradation due to increased accumulation of dark current.

If the integration time is changed while FRAME\_VALID is asserted for frame n, the first-frame output using the new integration time is frame (n + 2). The sequence is as follows:

- 1. During frame n, the new integration time is held in the pending register.

- 2. At the start of frame (n + 1), the new integration time is transferred to the live register. Integration for each row of frame (n + 1) has been completed using the old integration time.

- 3. The earliest time that a row can start integrating using the new integration time is immediately after that row has been read for frame (n + 1). The actual time that rows start integrating using the new integration time is dependent upon the new value of the integration time.

- 4. When frame (n + 2) is read out, it is integrated using the new integration time.

If the integration time is changed on successive frames, each value written will be applied for a single frame; the latency between writing a value and it affecting the frame readout remains at two frames.

When the integration time and the gain are changed at the same time, the gain update is held off by one frame so that the first frame output with the new integration time also has the new gain applied.

### **PLL**

### **PLL-Generated Master Clock**

The PLL can generate a master clock signal whose frequency is up to 80 MHz (input clock from 6 MHz through 54 MHz). R0x341C controls the frequency of the PLL-generated clock. It is possible to bypass the PLL and use CLKIN as master clock. In order to do so, one must set R0x341E[0] to "1." If power consumption is a concern, R0x341E[1] should be also set to "1" a short time later, to put the bypassed PLL in power-down mode. To enable the PLL again, the two bits must be set to "0" in the reverse order. By default, the PLL is bypassed and powered down.

### **PLL Setup**

Because the input clock frequency is unknown, the part starts with the PLL disabled. The PLL takes time to power up. During this time, the behavior of its output clock signal is not guaranteed. The PLL output frequency is determined by two constants, M and N, and the input clock frequency.

PLL programming and power-up sequence is as follows:

- Program PLL frequency settings, R0x341C (pll\_m, pll\_n) (master clock frequency is equal to fVCO\_pll/8). With default settings master clock frequency of 80 MHz is obtained with <sup>f</sup>CLKIN=16 MHz.

- 2. Power up PLL, R0x341E[1] = 0.

- 3. Wait for PLL settling time > 1ms.

- 4. Turn off PLL bypass, R0x341E[0] = 0.

Allow one complete frame to effect the correct integration time after enabling PLL.

**Note:** Before enabling PLL, ensure the slew rate is optimized for pads.

The default M and N values are for 16 MHz.

Note:

Any changes to PLL settings must be done with PLL bypassed (R0x341E[0]=1). Also, EXTCLK must remain at a stable frequency with no missing pulses to ensure correct PLL operation. If the clock frequency is changed (or if pulses are missed) while the PLL is enabled, sensor operation is UNDEFINED. Depending on the duration and magnitude of the disturbance, frame rate will drop, frames will be corrupted, and the sensor may become non-functional. The proper sequence for changing PLL settings is: bypass the PLL, change the PLL settings, wait at least 1ms, disable PLL bypass.

### Table 4: Frequency Parameters

| Frequency        | Equation                             | Min (MHz) | Max (MHz) |

|------------------|--------------------------------------|-----------|-----------|

| fIN              | _                                    | 6         | 54        |

| <sup>f</sup> PFD | <sup>f</sup> clkin /(pll_n+1)        | 2         | 20        |

| fVCO             | <sup>f</sup> clkin * pll_m/(pll_n+1) | 320       | 640       |

### **Readout Options**

The sensor core supports different readout options to modify the image before it is sent to the IFP. The readout can be limited to a specific window of the original pixel array.

For preview modes, the sensor core supports both skipping and pixel averaging in x and y directions.

By changing the readout direction the image can be flipped in the vertical and/or mirrored in the horizontal.

### **Window Size**

The image output size is set with registers  $x_addr_start$ ,  $x_addr_end$ ,  $y_addr_start$ , and  $y_addr_end$ . The edge pixels in the 1,616 x 1,216 array are present to avoid edge defects and should not be included in the visible window. Binning will change the image output size.

#### Readout Modes

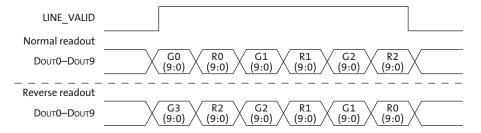

### **Horizontal Mirror**

When the horizontal\_mirror bit (R0x3040[0]) is set in the read mode register, the order of pixel readout within a row is reversed, so that readout starts from x\_addr\_end and ends at x\_addr\_start. Figure 7 on page 17 shows a sequence of 6 pixels being read out with horizontal\_mirror=0 and horizontal\_mirror=1. Changing horizontal\_mirror causes the Bayer order of the output image to change; the new Bayer order is reflected in the value of the pixel\_order register. This change in sensor core output is corrected for by the SOC.

Figure 7: 6 Pixels in Normal and Column Mirror Readout Modes

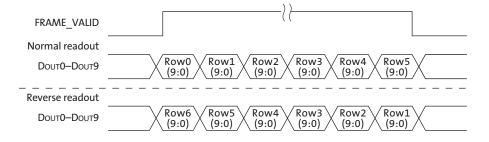

### **Vertical Flip**

When the vertical flip bit (R0x3040[1]) is set in the read mode register, the order in which pixel rows are read out is reversed, so that row readout starts from y\_addr\_end and ends at y\_addr\_start. Figure 8 shows a sequence of 6 rows being read out with row mirror=0 and row mirror=1. Changing vertical\_flip causes the Bayer order of the output image to change; the new Bayer order is reflected in the value of the pixel\_order register. This change in sensor core output is corrected for by the SOC.

Figure 8: 6 Rows in Normal and Row Mirror Readout Modes

### **Column and Row Skip**

The sensor core supports subsampling. Subsampling reduces the amount of data processed by the analog signal chain in the sensor and thereby allows the frame rate to be increased. Subsampling is enabled by setting x\_odd\_inc=3 and/or y\_odd\_inc=3. This reduces the amount of row and column data processed and is equivalent to the skip2 readout mode provided by earlier Aptina Imaging sensors. When enabling skipping, the proper image output and crop sizes must be updated beforehand.

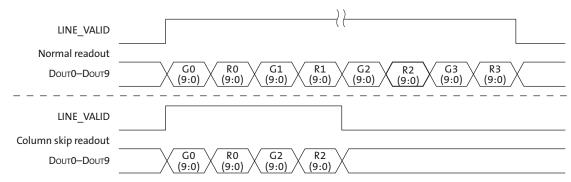

Figure 9: 8 Pixels in Normal and Column Skip 2X Readout Modes

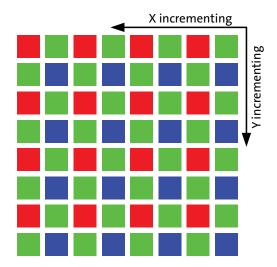

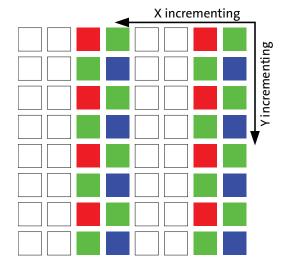

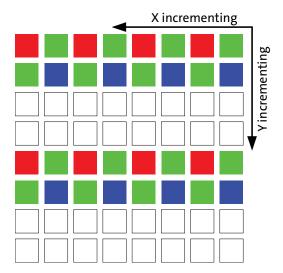

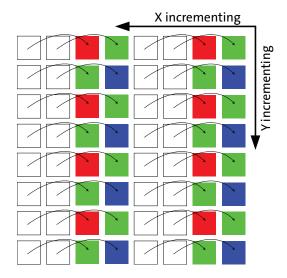

The following waveform shows a sequence of data being read out with x\_odd\_inc=3 and y\_odd\_inc=1. The effect of the different subsampling settings on the pixel array readout is shown in Figures 10 through 13.

Figure 10: Pixel Readout (no skipping)

Figure 11: Pixel Readout (x\_odd\_inc=3, y\_odd\_inc=1)

Figure 12: Pixel Readout (x\_odd\_inc=1, y\_odd\_inc=3)

Figure 13: Pixel Readout (x\_odd\_inc=3, y\_odd\_inc=3)

### **Programming Restrictions when Skipping**

When skipping is enabled as a viewfinder mode, and the sensor is switched back and forth between full resolution and skipping, it is recommended that line\_length\_pck be kept constant between the two modes. This allows the same integration times to be used in each mode.

When subsampling is enabled, it may be necessary to adjust the x\_addr\_end and y\_addr\_end settings. The values for these registers are required to correspond with rows/columns that form part of the subsampling sequence. The adjustment should be made in accordance with the following rule:

remainder = (addr\_end - addr\_start + 1) AND 4;

if (remainder == 0) addr\_end = addr\_end - 2;

Table 5 shows the row address sequencing for normal and subsampled (with y\_odd\_inc=3) readout. The same sequencing applies to column addresses for subsampled readout. There are two possible subsampling sequences (because the subsampling sequence only reads half of the rows and columns) depending upon the alignment of the start address.

Table 5: Row Address Sequencing

| Normal | Skipping<br>(start divides by 4) | Skipping<br>(start does not divide by 4) | Binned<br>(start divides by 4) | Binned<br>(start does not divide by 4) |

|--------|----------------------------------|------------------------------------------|--------------------------------|----------------------------------------|

| 0      | 0                                |                                          | 0, 2                           |                                        |

| 1      | 1                                |                                          | 1, 3                           |                                        |

| 2      |                                  | 2                                        |                                | 2, 4                                   |

| 3      |                                  | 3                                        |                                | 3, 5                                   |

| 4      | 4                                |                                          | 4, 6                           |                                        |

| 5      | 5                                |                                          | 5, 7                           |                                        |

| 6      |                                  | 6                                        |                                | 6, 8                                   |

| 7      |                                  | 7                                        |                                | 7, 9                                   |

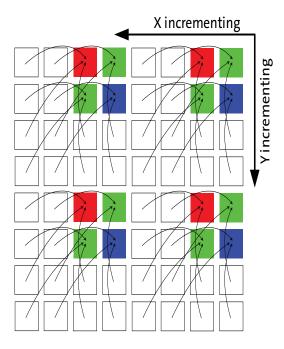

### **Binning**

The MT9D112 sensor core supports 2x1 and 2x2 analog binning (column binning, also called x-binning and row/column binning, also called xy-binning). Binning has many of the same characteristics as subsampling but because it gathers image data from all pixels in the active window (rather than a subset of them), it achieves superior image quality and avoids the aliasing artifacts that can be a characteristic side effect of subsampling.

Binning is enabled by selecting the appropriate subsampling settings (x\_odd\_inc=3 and y\_odd\_inc=1 for x-binning, x\_odd\_inc=3 and y\_odd\_inc=3 for xy-binning) and setting the appropriate binning bit in read\_mode (R0x3040-1). As for subsampling, x\_addr\_end and y\_addr\_end may require adjustment when binning is enabled.

The effect of the different subsampling settings is shown in Figure 14 and Figure 15.

Figure 14: Pixel Readout (x odd inc=3, y odd inc=1, x bin=1)

Figure 15: Pixel Readout (x\_odd\_inc=3, y\_odd\_inc=3, x\_ybin=1)

### **Binning Limitations**

Binning requires different sequencing of the pixel array and imposes different timing limits on the operation of the sensor. In particular, xy-binning requires two read operations from the pixel array for each line of output data, which has the effect of increasing the minimum line blanking time.

As a result, when xy-binning is enabled, some of the programming limits declared in the parameter limit registers are no longer valid. In addition, the default values for some of the manufacturer-specific registers need to be reprogrammed. None of these adjustments are required for x-binning. The sensor must be taken out of streaming mode before switching between binned and non-binned operation.

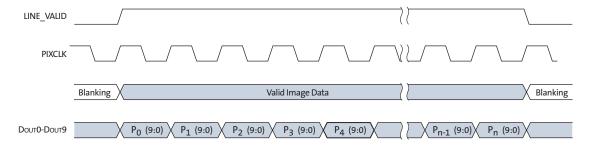

### **Raw Data Format**

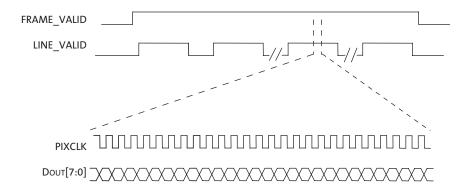

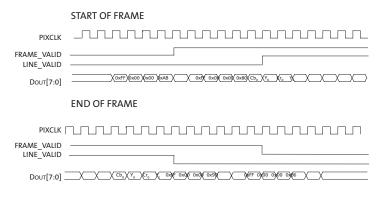

The sensor core image data is read out in a progressive scan. Valid image data is surrounded by horizontal blanking and vertical blanking as shown in Figure 16. The amount of horizontal blanking and vertical blanking is programmable. LINE\_VALID is HIGH during the shaded region of the figure. FRAME\_VALID timing is described in the next section.

Figure 16: Pixel Data Timing Example

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 00 00 00 00 00 00<br>00 00 00        |  |

|------------------------------------------------------|--------------------------------------|--|

| VALID IMAGE                                          | HORIZONTAL<br>BLANKING               |  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 00 00 00 00 00 00                    |  |

| 00 00 0000 00 00<br>00 00 0000 00 00                 | 00 00 0000 00 00<br>00 00 0000 00 00 |  |

| VERTICAL BLANKING                                    | VERTICAL/HORIZONTAL                  |  |

|                                                      | BLANKING                             |  |

## **Raw Data Timing**

The sensor core output data is synchronized with the PIXCLK output. When LINE\_VALID is HIGH, one pixel data is output on the 10-bit Dout output every PIXCLK period. By default, the PIXCLK signal runs at half the frequency as the master clock, and its falling edges occur one master clock period (half PIXCLK period) after transitions on LINE\_VALID, FRAME\_VALID, and Dout (Figure 17). This allows PIXCLK to be used as a clock to sample the data. PIXCLK is continuously enabled, even during the blanking period.

Figure 17: Pixel Data Timing Example

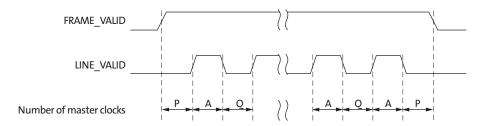

Figure 18: Row Timing and FRAME\_VALID/LINE\_VALID Signals

The sensor timing is shown in terms of pixel clock and master clock cycles (Figure 17 and Figure 18). Increasing the integration time to more than one frame causes the frame time to be extended.

Table 6: Row Timing Parameters

| Parameter     | Name                      |         | Equation                                                | Default at CLKIN = 54 MHz<br>(PLL Off) |

|---------------|---------------------------|---------|---------------------------------------------------------|----------------------------------------|

|               |                           | PLL Off | 2*R0x3016[2:0]/ <sup>f</sup> CLKIN                      |                                        |

| PIXCLK_PERIOD | Pixel clock period        | PLL On  | (16*R0x3016[2:0]*(pll_n+1))/( <sup>f</sup> CLKIN*pll_m) | 1 pixel clock = 37.04ns                |

| S             | Skip (subsampling) factor |         | For x_odd_inc=y_odd_inc=3, S=2<br>Otherwise, S=1        | 1                                      |

| Α             | Active data time          |         | (x_addr_end-x_addr_start+1)*PIXCLK_PERIOD/S             | 1,608 pixel clocks = 59.56?s           |

| Р             | Frame start/end blanking  |         | 6*PIXCLK_PERIOD                                         | 6 pixel clocks = 222.22ns              |

| Q             | Horizontal blanking       |         | (line_length_pck*PIXCLK_PERIOD)-A                       | 476 pixel clocks = 17.63μs             |

| A + Q         | Row time                  |         | line_length_pck*PIXCLK_PERIOD                           | 2,084 pixel clocks = 77.19μs           |

| N             | Number of rows            |         | (y_addr_end-y_addr_start +1)/S                          | 1,208 rows                             |

| V             | Vertical blanking         |         | ([frame_length_lines-N]*[A+Q])+Q-(2*P)                  | 110,916 pixel clocks = 4.108ms         |

| Tfv           | Frame valid time          |         | (N*(A+Q))-Q+(2*P)                                       | 2,517,008 pixel clocks = 93.22ms       |

| F             | Total frame time          |         | line_length_pck*frame_length_lines*PIXCLK_PERIOD        | 2,627,924 pixel clocks = 97.33ms       |

# **SOC Description**

# **Image Flow Processor**

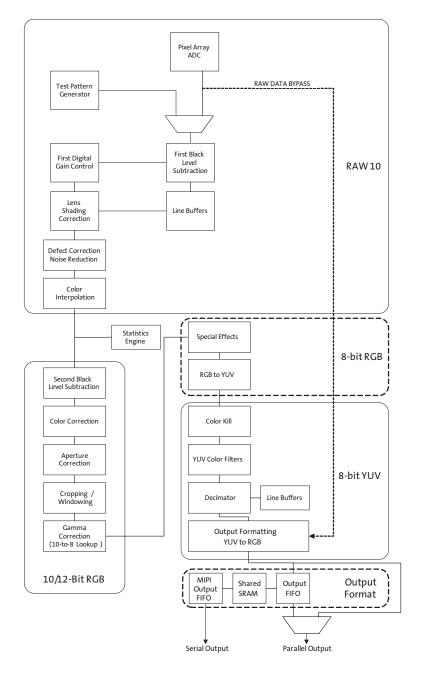

Image and color processing in the MT9D112 is implemented as an image flow processor coded in hardware logic. The IFP can be controlled by registers from the outside but during normal operation, the embedded microcontroller will automatically adjust the operation parameters. The IFP is broken down into different sections outlined in Figure 19.

Figure 19: Color Pipeline

### **Test Patterns**

During normal operation of the MT9D112, a stream of raw image data from the sensor core is continuously fed into the color pipeline. For test purposes, this stream can be replaced with a fixed image generated by a special test module in the pipeline. The module provides a selection of test patterns sufficient for basic testing of the pipeline.

Test patterns are accessible using R0x3290 and are shown in Figure 20. Disabling MCU is recommended before enabling test patterns.

Figure 20: Test Patterns

|   | Test Pattern     | Register Value | Example |

|---|------------------|----------------|---------|

| • | Flat Field       | R0x3290 = 1    |         |

|   | Vertical Ramp    | R0x3290 = 2    |         |

|   | Color Bar        | R0x3290 = 3    |         |

|   | Vertical Stripes | R0x3290 = 4    |         |

|   | Pseudo-Random    | R0x3290 = 5    |         |

### First Black Level Subtraction and Digital Gain

Image stream processing starts with black level subtraction (R0x3278) and multiplication of all pixel values by a programmable digital gain (R0x32DC). Both operations can be independently set to separate values for each color channel (R, Gr, Gb, B). Independent color channel digital gain is adjusted with registers R0x32D4 through R0x32DA. Independent color channel black level adjustments can be made with R0x327A through R0x3280. If the black level subtraction produces a negative result for a particular pixel, the value of this pixel is set to "1."

### **Lens Shading Correction**

Lenses tend to produce images whose brightness is significantly attenuated near the edges. There are also other factors causing fixed pattern signal gradients in images captured by image sensors. The cumulative result of all these factors is known as lens shading. The MT9D112 has an embedded lens shading correction (LC) module that can be programmed to counter the shading effect of a lens on each individual R, Gb, Gr, and B color signal. The LC module multiplies R, Gb, Gr, and B signals by a 2-dimensional correction function F (x,y), whose profile in both x and y direction is a piecewise quadratic polynomial with coefficients independently programmable for each direction and color. Lens shading correction can be enabled and disabled with R0x3210[2].

The MT9D112 also includes 16 independent corner parameters, K, for each of the color channels. The K factors are independently adjustable at each corner and are not dependent on the vertical and horizontal spatial dimension. They can be adjusted with R0x3544 through R0x3562.

Lens shading correction can be enabled and disabled with R0x3210[2].

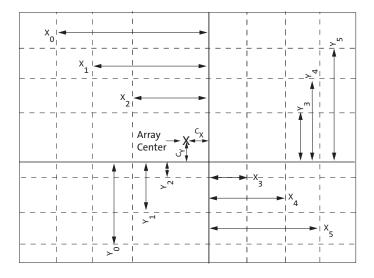

### **Lens Correction Zones**

In order to increase the precision of the correction function, the image plane is divided into 8 zones in each dimension. The coordinates of zone boundaries are referenced with respect to the lens center, C. Each boundary as well as C (Cx, Cy) coordinate is stored as a byte, which represents the coordinate value divided by 4. There always three boundaries to the left (top) of the center and three to the right (bottom) of the center. These boundaries apply uniformly for all color channels. However, the correction functions are programmable independently for each color component. Boundary and lens center positions are also valid for the preview mode. Figure 21 on page 27 illustrates the lens correction zones, which are accessible through registers R0x34CE through R0x34DC.

Figure 21: Lens Correction Zones

#### **Defect Correction and Noise Reduction**

The IFP performs on-the-fly defect correction that can mask pixel array defects such as high dark current (hot) pixels and pixels that are darker or brighter than their neighbors due to photoresponse nonuniformity. Each pixel is compared with its 8 nearest neighbors having the same filter color. Suppose the value of the compared pixel is P and the values of the 8 neighbors range from PMIN to PMAX. If P > PMAX, P is replaced with PMAX. Likewise, if P < PMIN, P is replaced with PMIN. Otherwise, the pixel is not considered defective, and its value P is not changed. Defect correction can be enabled and disabled with R0x3210[3].

The image data for each color channel can be passed through an adaptive noise suppression module which averages over flat field areas while preserving edge information. The module is edge aware with exposure that is based on configurable thresholds. The thresholds are changed on the fly based on the brightness of the current scene. Noise reduction can be enabled and disabled with R0x33F4[3] and thresholds are set by R0x33F6 through R0x33FC.

#### **Color Interpolation and Edge Detection**

In the raw data stream fed by the sensor core to the IFP, each pixel is represented by a 10-bit integer number, which can be considered proportional to the pixel's response to a one-color light stimulus, red, green or blue, depending on the pixel's position under the color filter array. Initial data processing steps, up to and including the defect correction, preserve the 1-color-per-pixel nature of the data stream, but after the defect correction it must be converted to a 3-colors-per-pixel stream appropriate for standard color processing. The conversion is done by an edge-sensitive color interpolation module. The module pads the incomplete color information available for each pixel with information extracted from an appropriate set of neighboring pixels. The algorithm used to select this set and extract the information seeks the best compromise between preserving edges and filtering out high frequency noise in flat field areas. The edge threshold can be set with R0x328E.

#### **Second Black Level Correction**

After interpolation it might be necessary to recalibrate the black level. A second global black level substraction is possible at this stage in the pipeline, which is controlled via R0x3276. If the subtraction produces a negative result for a particular pixel, the value of this pixel is set to "0."

### **Color Correction and Aperture Correction**

To achieve good color fidelity of IFP output, interpolated RGB values of all pixels are subjected to color correction. The IFP multiplies each vector of three pixel colors by a 3 x 3 color correction matrix. The three components of the resulting color vector are all sums of three 10-bit numbers. Since such sums can have up to 12 significant bits, the bit width of the image data stream is widened to 12 bits per color (36 bits per pixel). The color correction matrix can be either programmed by the user or automatically selected by the auto white balance (AWB) algorithm implemented in the IFP. Color correction should ideally produce output colors that are independent of the spectral sensitivity and color crosstalk characteristics of the image sensor. The optimal values of color correction matrix elements depend on those sensor characteristics and on the spectrum of light incident on the sensor. The color correction variables can be adjusted with R0x006 through R0x042.

To increase image sharpness, a programmable 1D or 2D aperture correction (sharpening filter) is applied to color corrected image data. Aperture correction is enabled using R0x3210. The gain and threshold for 1D and 2D correction can be defined via R0x326A and R0x326C.

### **Image Cropping**

Image cropping takes place when the sensor core is programmed to output pixel values from a rectangular portion of its pixel array-a window-smaller than the default 1,600 x 1,200 window. Pixels outside the selected cropping window are not read out, resulting in a narrower field of view than at the default sensor settings. Irrespective of the size and position of the cropping window, the MT9D112 sensor core can also decimate outgoing images by skipping columns and/or rows of the pixel array, and/or by binning 2 x 2 groups of pixels of the same color. Since scaling by skipping (deletion) can cause aliasing (even if pixel binning is simultaneously enabled), it is generally better to change image size only by cropping and pixel binning.

In context A, the cropped window is defined by variables 0x051 through 0x057. In context B, it is defined by 0x05F and 0x065. In context A and B, the height and width definitions for the output window must be equal to or smaller than the cropped image.

Output width will always be as with no scaling; crop will still be in effect.

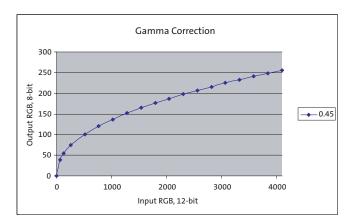

### **Contrast and Gamma Correction**

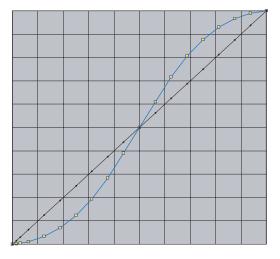

Gamma correction is independently applied and independently configurable for each of the 12-bit R, G, and B color channels. The gamma correction curve is implemented as a piecewise linear function with 19 knee points, taking 12-bit arguments and mapping them to 8-bit output. The abscissas of the knee points are fixed at 0, 64, 128, 256, 512, 768, 1024, 1280, 1536, 1792, 2048, 2304, 2560, 2816, 3072, 3328, 3584, 3840, and 4096. The 8-bit ordinates are programmable through the IFP registers.

The MT9D112 IFP includes a block for gamma and contrast correction. A custom gamma/contrast correction table may be uploaded, or preset gamma and contrast settings may be selected.

The gamma and contrast correction block uses the following 12-bit input data points to form a piecewise linear transformation curve: 0, 64, 128, 256, 512, 768, 1024, 1280, 1536, 1792, 2048, 2304, 2560, 2816, 3072, 3328, 3584, 3840, and 4096. These input points have been selected to provide more detail to the low end of the curve where gamma correction changes are typically the greatest. These points correspond to 8-bit output values that can be uploaded to the appropriate registers.

Figure 22: Gamma Correction Curve

For simplicity, predefined gamma and contrast tables may be selected, and the MT9D112 automatically combines these tables and upload them to the appropriate gamma correction registers.

The gamma and contrast tables may be selected at mode driver (ID = 7) offsets 109 and 110 (decimal) for context A and context B, respectively. The gamma settings are established at bits 0-2, and the contrast settings are established at bits 4-6.

The gamma setting values are shown in Table 7.

Table 7: Gamma Settings

| Gamma Setting | Definition                        |  |

|---------------|-----------------------------------|--|

| 0             | Gamma = 1.0 (no gamma correction) |  |

| 1             | Gamma = 0.56                      |  |

| 2             | Gamma = 0.45                      |  |

| 3             | Use user-defined gamma table      |  |

#### **S-Curve**

The predefined contrast table values have been established by creating an "S" curve with highlight and shadow regions that blend smoothly with a linear midtone region. The slope and value of the highlight and shadow regions match the linear region at these transitions. In addition, the slope of the "S" curve is zero at the top (white) and bottom (black) points. The slope of the linear region determines how much contrast is applied; more contrast corresponds to a higher, midtone linear slope.

Figure 23: Contrast "S" Curve

Table 8: Contrast Values

| Contrast Setting | Definition               |

|------------------|--------------------------|

| 0                | No contrast correction   |

| 1                | Contrast slope = 1.25    |

| 2                | Contrast slope = 1.50    |

| 3                | Contrast slope = 1.75    |

| 4                | Noise reduction contrast |

The contrast curve function is applied to the gamma curve points used (whether the gamma curve points are predefined or user-uploaded).

S-curve is a function to correct image pixel values. When applied to pixel values, it typically compresses dark and bright tones, while stretching the midtones.

Special effects like negative image, sepia, or B/W can be applied to the data stream at this point. Special effects are enabled with R0x3348.

### **RGB to YUV Conversion**

For further processing the data is converted from RGB color space to YUV color space.

#### **Color Kill**

To remove high light or low light color artifacts, a color kill circuit is included. It affects only pixels whose luminance exceeds a certain preprogrammed threshold. The U and V values of those pixels are attenuated proportionally to the difference between their luminance and the threshold.

#### **YUV Color Filter**

As an optional processing step noise suppression by 1-dimensional low-pass filtering of Y and/or UV signals is possible. A 3- or 5-tap filter can be selected for each signal.

### **Image Scaling**

To ensure that the size of images output by the MT9D112 can be tailored to the needs of all users, the IFP includes a scaler module. When enabled, this module performs rescaling of incoming images—shrinks them to arbitrarily selected width and height without reducing the field of view and without discarding any pixel values.

The scaler performs pixel binning—divides each input image into rectangular bins corresponding to individual pixels of the desired output image, averages pixel values in these bins, and assembles the output image from the bin averages. Pixels lying on bin boundaries contribute to more than one bin average: their values are added to bin-wide sums of pixel values with fractional weights. The entire procedure preserves all image information that can be included in the downsized output image and filters out high frequency features that could cause aliasing.

The image cropping and scaler module can be used together to implement a digital zoom and pan. If the scaler is programmed to output images smaller than images coming from the sensor core, zoom effect can be produced by cropping the latter from their maximum size down to the size of the output images. The ratio of these two sizes determines the maximum attainable zoom factor. For example, a 1,600 x 1,200 image rendered on a 160 x 120 display can be zoomed up to 10 times, since 1,600/160 = 1,200/120 = 10. Panning effect can be achieved by fixing the size of the cropping window and moving it around the pixel array.

Due to the loss of sharpness due to pixel binning during image scaling, 1D aperture correction may be applied to increase image sharpness lost due to pixel binning during image scaling.

# YUV-to-RGB/YUV Conversion and Output Formatting

The YUV data stream emerging from the scaler module can either exit the color pipeline as-is or be converted before exit to an alternative YUV or RGB data format as selected by R0x332E.

#### **Color Conversion Formulas**

### Y'U'V'

This conversion is BT 601 scaled to make YUV range from 0 through 255. This setting is recommended for JPEG encoding and is the most popular, although it is not well defined and is often misused in Windows.

$$\begin{split} Y' &= 0.299 \; R' + 0.587 \; G' + 0.114 \; B' \\ U' &= 0.564 \; (B' - Y') + 128 \\ V' &= 0.713 \; (R' - Y') + 128 \end{split}$$

There is an option where 128 is not added to U'V'.

### Y'Cb'Cr' Using sRGB Formulas

The MT9D112 implements the sRGB standard. This option provides YCbCr coefficients for a correct 4:2:2 transmission. Note that  $16 < Y60 \le 1 < 235$ , 16 < Cb, Cr < 240 and 0 < 1 < 100 RGB 0 < 100 RGB 0 < 1 < 100 RGB 0 < 100 RGB 0 < 1 < 100 RGB 0 < 1

$$Y' = (0.2126*R' + 0.7152*G' + 0.0722*B')*219/256 + 16$$

Cb' = 0.5389\*(B'-Y')\*224/256 + 128

Cr' = 0.635\*(R' - Y')\*224/256 + 128

### Y'U'V' Using sRGB Formulas

Similar to the previous set of formulas, but has YUV spanning a range of 0 through 255.

$$Y' = 0.2126*R' + 0.7152*G' + 0.0722*B'$$

$$U' = 0.5389*(B' - Y') + 128 = -0.1146*R - 0.3854*G + 0.5*B$$

$$V' = 0.635*(R' - Y') + 128 = 0.5*R - 0.4542*G - 0.0458*B$$

There is an option to disable adding 128 to U'V'. The reverse transform is as follows:

$$R' = Y + 1.5748*V$$

$$G' = Y - 0.1873*(U - 128) - 0.4681*(V - 128)$$

$$B' = Y + 1.8556*(U - 128)$$

# **Output Interface**

### **Parallel and MIPI Output**

The user can select to either use the serial MIPI output or the 8-bit parallel output to transmit the data. Only one of the output modes can be used at any time.

The parallel output, enabled by R0x301A[7], can be used with an output FIFO whose memory is shared with the MIPI output FIFO to retain a constant pixel output clock independent from the scaling factor.

When scaling the image or skipping lines, the data would be generated in bursts and the pixel clock would turn on and off in intervals, which might lead to EMI problems. The output FIFO will group all active pixel data together so the pixel clock can be run at a constant speed. The output FIFO is enabled by setting R0x3212[1:0] to 10. There are two registers to configure the output FIFO, watermark and line length.

The MIPI output transmitter implements a fully configurable serial differential subLVDS transmitter capable of up to  $640~\rm Mb/s$ . It supports multiple formats, error checking, and custom short packets.

### **Output Format and Timing**

### YUV/RGB Uncompressed Output

Uncompressed YUV or RGB data can be output either directly from the output formatting block or through a FIFO buffer with a capacity of 800 bytes, enough to hold one-fourth of an uncompressed line at full resolution. Buffering of data is a way to equalize the data output rate when image scaling is used. Scaling produces an intermittent data stream consisting of short high-rate bursts separated by idle periods. High pixel clock frequency during bursts may be undesirable due to EMI concerns.

Figure 24 on page 33 depicts the output timing of uncompressed YUV/RGB when a decimated data stream is equalized by buffering or when no scaling takes place. The pixel clock frequency remains constant during each LINE\_VALID HIGH period. Decimated data are output at a lower frequency than full size frames, which helps to reduce EMI.

Figure 24: Timing of Uncompressed Full Frame Output or Decimated Output Passing Through the FIFO

### **Uncompressed YUV/RGB Data Ordering**

The MT9D112 supports swapping YCrCb mode, as illustrated in Table 9.

Table 9: YCrCb Output Data Ordering

| Mode              |                 |                 |                  |                  |

|-------------------|-----------------|-----------------|------------------|------------------|

| Default (no swap) | Cb <sub>i</sub> | Yi              | Cr <sub>i</sub>  | Y <sub>i+1</sub> |

| Swapped CrCb      | Cr <sub>i</sub> | Yi              | Cb <sub>i</sub>  | Y <sub>i+1</sub> |

| Swapped YC        | Yi              | Cb <sub>i</sub> | Y <sub>i+1</sub> | Cr <sub>i</sub>  |

| Swapped CrCb, YC  | Yi              | Cr <sub>i</sub> | Y <sub>i+1</sub> | Cb <sub>i</sub>  |

The RGB output data ordering in default mode is shown in Table 10. The odd and even bytes are swapped when luma/chroma swap is enabled. R and B channels are bit-wise swapped when chroma swap is enabled.

Table 10: RGB Ordering in Default Mode

| Mode (Swap Disabled) | Byte | $D_7D_6D_5D_4D_3D_2D_1D_0$                                           |

|----------------------|------|----------------------------------------------------------------------|

| RGB 565              | Odd  | $R_7R_6R_5R_4R_3G_7G_6G_5$                                           |

|                      | Even | $G_4G_3G_2B_7B_6B_5B_4B_3$                                           |

| RGB 555              | Odd  | $0 R_7 R_6 R_5 R_4 R_3 G_7 G_6$                                      |

|                      | Even | $G_4G_3G_2B_7B_6B_5B_4B_3$                                           |

| RGB 444x             | Odd  | $R_7R_6R_5R_4G_7G_6G_5G_4$                                           |

|                      | Even | B <sub>7</sub> B <sub>6</sub> B <sub>5</sub> B <sub>4</sub> 0 0 0 0  |

| RGB x444             | Odd  | 0 0 0 0 R <sub>7</sub> R6 <sub>6</sub> R <sub>5</sub> R <sub>4</sub> |

|                      | Even | $G_7G_6G_5G_4B_7B_6B_5B_4$                                           |

### **Uncompressed 10-Bit Bypass Output**

Raw 10-bit Bayer data from the sensor core can be output in bypass mode in two ways:

- 1. Using 8 data output pads (DOUTO-DOUT7), and GPIO[0:1].

- 2. Using only 8 pads (DOUTO-DOUT7) and a special 8 + 2 data format, shown in Table 11.

The timing of 10-bit or 8-bit data stream output in the bypass mode is qualitatively the same as that depicted in Figure 25 on page 34.

Table 11: 2-Byte RGB Format

| Odd bytes  | 8 data bits                 | $D_9D_8D_7D_6D_5D_4D_3D_2$         |

|------------|-----------------------------|------------------------------------|

| Even bytes | 2 data bits + 6 unused bits | 00000D <sub>1</sub> D <sub>0</sub> |

Figure 25: Example of Timing for Non-Decimated Uncompressed Output Bypassing Output FIFO

**FIFO**

During normal pipeline operation the output data rate is determined by a number of factors, for instance, input image size, degree of scaling, and sensor operation mode. As these parameters change during normal sensor operation, output frequency changes. This output frequency may generate RF noise, interfering with the mobile device. By using an output FIFO to maintain a constant output clock frequency, noise is easily filtered out.

The FIFO accumulates data and after a certain number of bytes are stored, it will yield them in a single burst making sure that data rate within the burst remains constant. This approach may utilize a free running clock thus minimizes possible RF interference.

In the default operation the mode user must provide two values for proper FIFO operation:

- 1. the expected line length (R0x3220)

- 2. watermark (R0x321E)

The value for both has to be specified in bytes. Calculation of line length is straightforward; multiply the number of pixels by the number of bytes per pixel. The number of bytes per pixel is 2 for all output modes except processed Bayer in which it equals one byte per pixel.

### Watermark

Calculation of the watermark should be done based on the maximum number of bytes that the pipeline could output in the given mode (with activated clip and no scaling) and the number of bytes it will yield, taking into account scaling. Also, accounting for the horizontal sensor binning mode if it is activated. In this mode, the number of pixels that the pipeline can output should be doubled.

### **Camera Control**

# **General Purpose I/Os**

The four general purpose I/Os of the MT9D112 can be configured in multiple ways. Each of the I/Os can be used as a simple input/output that can be programmed from the host. The status of the GPIO is read at power up and can be used as a module ID to separate different module suppliers.

If 10-bit RAW output is required, GPIO[1:0] can be configured as bit 0 and bit 1 of a 10-bit data bus.

GPIO[3:2] can be configured to output a flash pulse to trigger an external Xenon or LED flash or a shutter pulse to control an external shutter.

The general purpose inputs are enabled by setting R0x301A[8]. Once enabled, all four inputs must be driven to valid logic levels by external signals. The state of the general purpose inputs can be read through R0x3026[3:0].

In addition, each of the following functions can be associated with none, one, or more of the general purpose inputs so that the function can be directly controlled by a hardware input:

- Output enable

- Trigger

- Standby functions

The gpi\_status register is used to associate a function with a general purpose input.

### **Output Enable Control**

When the parallel pixel data interface is enabled, its signals can be switched asynchronously between the driven and High-Z under pin or register control, as shown in Table 12.

**Table 12:** Output Enable Control

| OE_BAR Pin | Drive Signals<br>R0x301A[6] | Description      |

|------------|-----------------------------|------------------|

| Disabled   | 0                           | Interface High-Z |

| Disabled   | 1                           | Interface driven |

| 1          | 0                           | Interface High-Z |

| X          | 1                           | Interface driven |

| 0          | Х                           | Interface driven |

### **Trigger Control**

When the global reset feature is in use, the trigger for the sequence can be initiated either under pin or register control, as shown in Table 13.

Table 13: Trigger Control

| TRIGGER  | Global Trigger R0x3060-1[0] | Description |

|----------|-----------------------------|-------------|

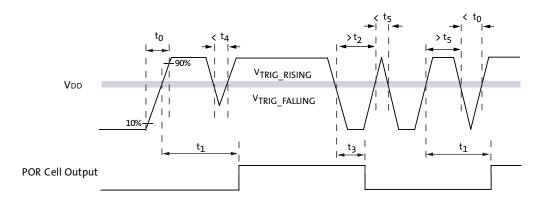

| Disabled | 0                           | Idle        |